A Generic VHDL-AMS Behavioral Model Physically Accounting For Analog Non-Linear Output Behavior

Kamal Sabet Tamer Riad

#### Outline

#### Introduction

- Modeling AMS Systems

- Analog Output Behavior

- Conventional Modeling Approach

- Circuit Inspired Approach

- Model Implementation

- Experimental Results

- Application

- Conclusion

#### Introduction

Mixed-signal verification has proved essential for debugging today's integrated SOCs.

To assert the integral operation of the entire system, several top-level simulations have to be performed.

Extensive computational cost and design immaturity require top-level simulation to be performed beyond the realm of SPICE kernels.

# **Modeling AMS Systems**

- A valid AMS system's models must capture the correct functionality of their corresponding blocks.

- In addition, accurate interfacing must correctly account for the correct impedance at the peripheral terminals.

- This becomes a challenge when functionality and loading are interdependent.

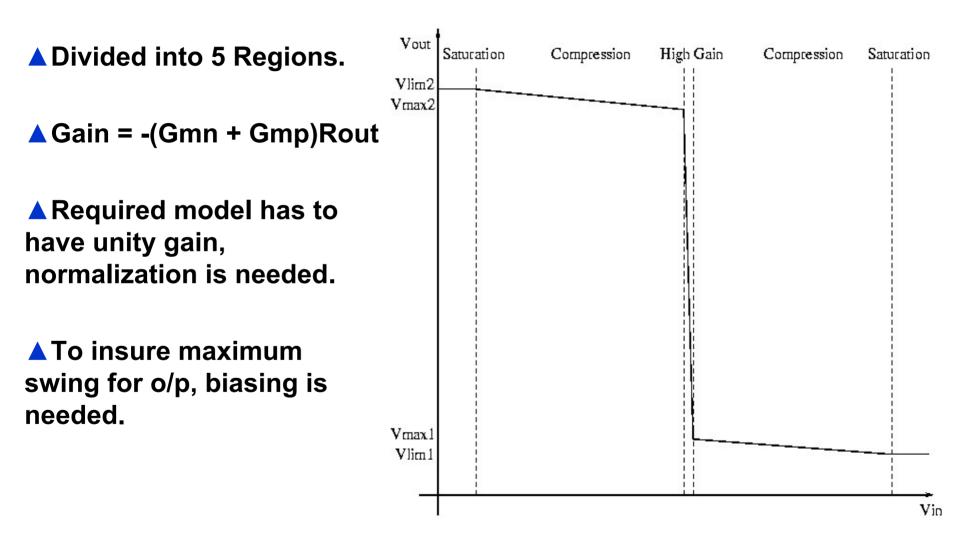

# **Analog Output Behavior**

#### Common output characteristics

- Output voltage saturation

- ▲ Output resistance

- ▲ Output DC level

- ▲ Output capacitance

- Output current limiting

# Modeling Voltage Saturation & Output Resistance

Has to be valid in both linear and non-linear operation.

The value of output resistance should change from one mode of operation to the other.

Assuming it to be the same, will yield erroneous results, which would restrains the use of this model.

## **Conventional Modeling Approach**

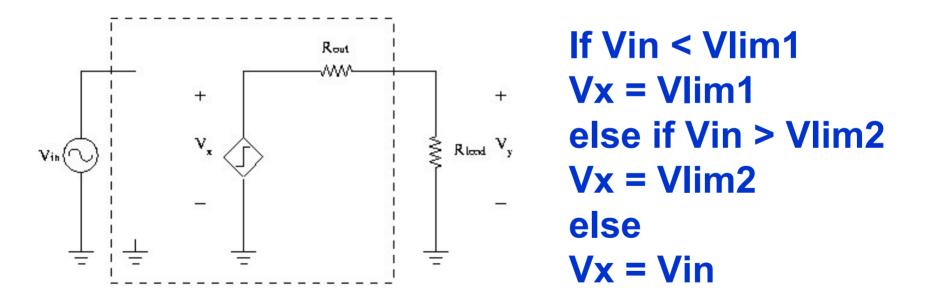

The controlled source  $V_x$  is used to decide on the output voltage  $V_y$  depending on  $V_{in}$ .

#### Conventional Modeling Approach (cont'd)

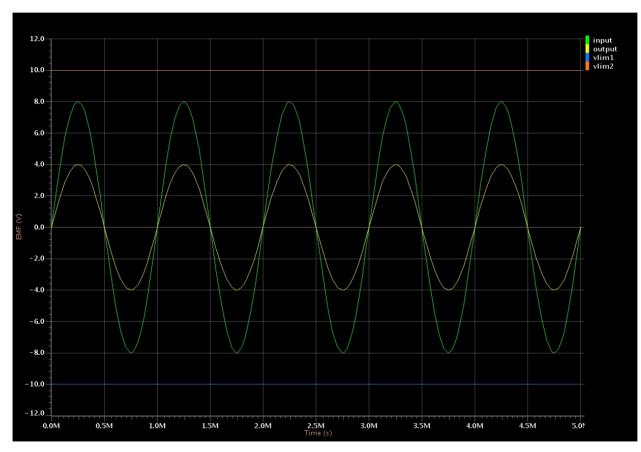

During linear operation,  $V_y$  will be evaluated by voltage division of  $V_{in}$  between  $R_{load}$  and  $R_{out}$

#### Conventional Modeling Approach (cont'd)

During non-linear operation, voltage division will result in a signal saturated at levels below the desired output limits.

# **Circuit Inspired Approach**

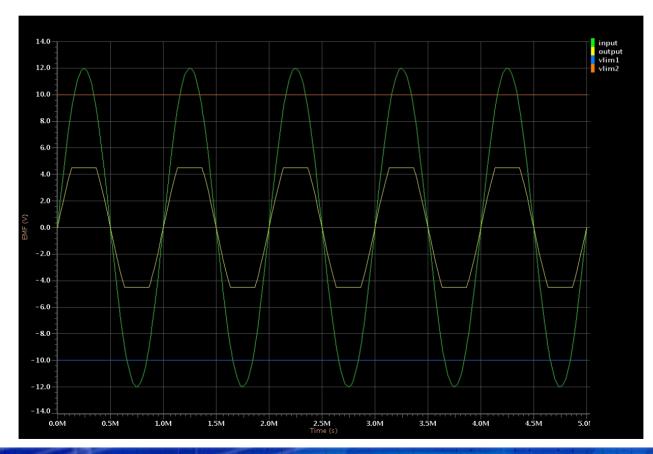

- Assumed circuit comprises of 2 hypothetical MOS-like devices connected in a push-pull topology.

- Input common to both gates, output at their drains.

- Power supplies are the limiting voltages.

## **Simplified Device Models**

Circuit inspired approach uses Abstracted transistors.

Expresses Basic transistor action.

Preserves relations between model parameters and device parameters.

Starting point is MOS level 1 equations.

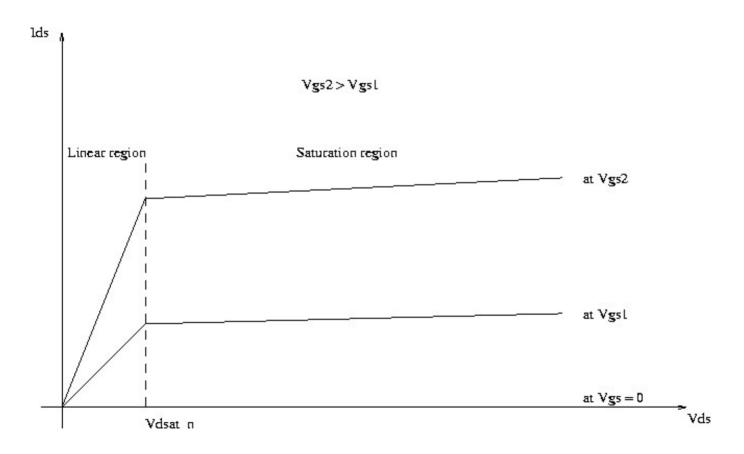

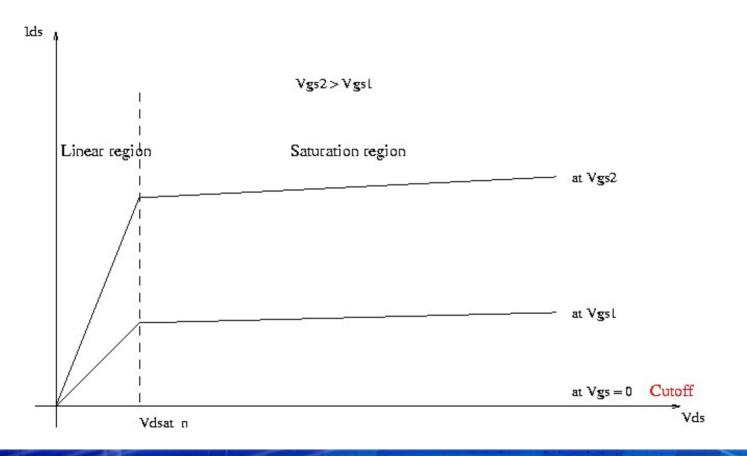

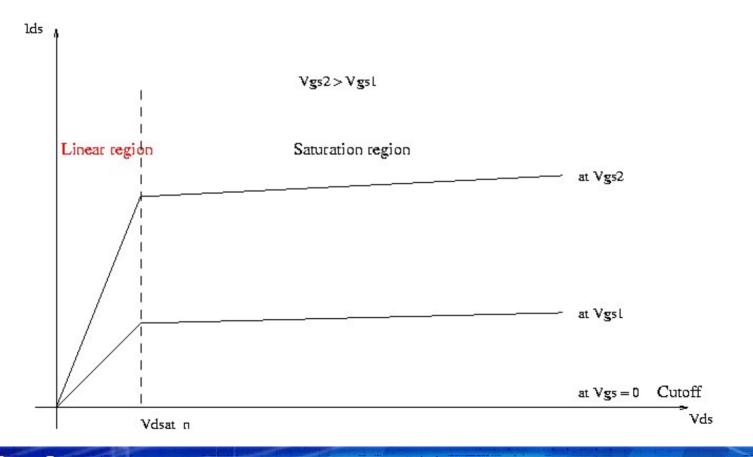

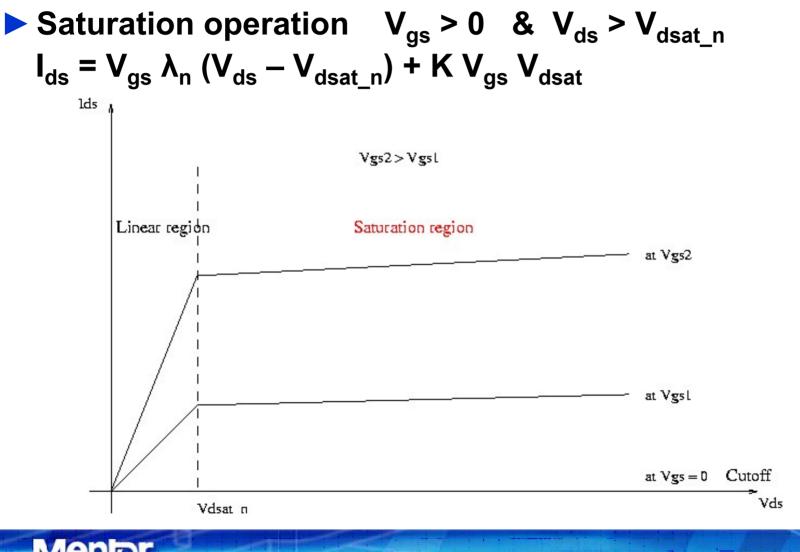

#### **Device I-V Characteristics**

# 3 Regions of operation 2 Linear Equations

# Cutoff operation V<sub>gs</sub> < 0</p> I<sub>ds</sub> = 0

**BMAS 2007**

# Linear operation V<sub>gs</sub> > 0 & V<sub>ds</sub> < V<sub>dsat\_n</sub> I<sub>ds</sub> = K V<sub>gs</sub> Vds (V<sub>dsat</sub> / V<sub>dsat\_n</sub>)

Linear operation

$$V_{gs} > 0 \& V_{ds} < V_{dsat_n}$$

$I_{ds} = K V_{gs} V_{ds} (V_{dsat} / V_{dsat_n})$

Where; ▲K : relates I<sub>ds</sub> to V<sub>gs</sub> = 1 S/V for simplicity

#### ▲ V<sub>dsat\_n</sub> : Defines onset of saturation

▲ V<sub>dsat</sub> = (V<sub>dsat\_n</sub> + V<sub>dsat\_p</sub>)/2 : Used to balance Idsat for both devices.

For the same V<sub>gs</sub>\V<sub>sg</sub>: I<sub>dsat</sub> = V<sub>gs</sub>\V<sub>gs</sub> V<sub>dsat</sub>

Saturation operation for  $V_{gs} > 0 \& V_{ds} > V_{dsat_n}$  $I_{ds} = V_{gs} \lambda_n (V_{ds} - V_{dsat_n}) + K V_{gs} V_{dsat}$

Where;

▲  $λ_{n:}$  Controls device output resistance in saturation  $R_{sat_n} = \delta V_{ds} / \delta I_{ds} = 1 / (V_{gs} λ_{n})$

Δ Device transconductance G<sub>mn</sub> = λ<sub>n</sub>(V<sub>ds</sub> – V<sub>dsat\_n</sub>) + KV<sub>dsat</sub>

\*  $G_{mn}$  independent of  $V_{gs}$

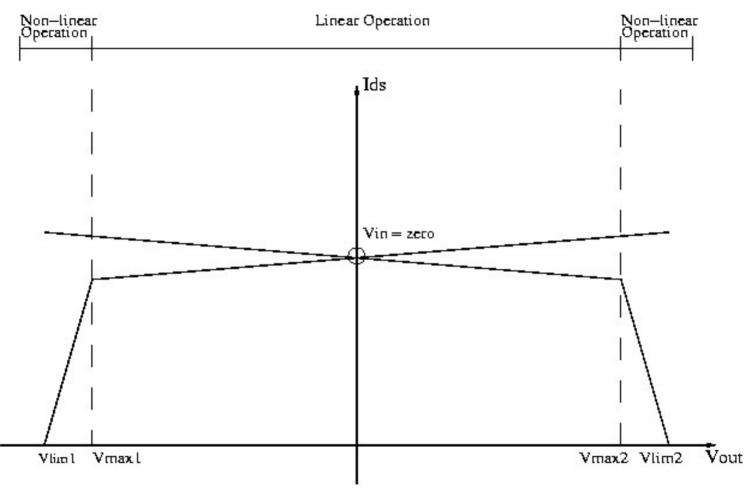

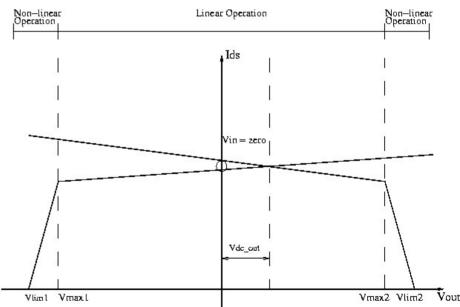

# **Large Signal Behavior**

$$V_{in}=0, V_{gs}=V_{sg}$$

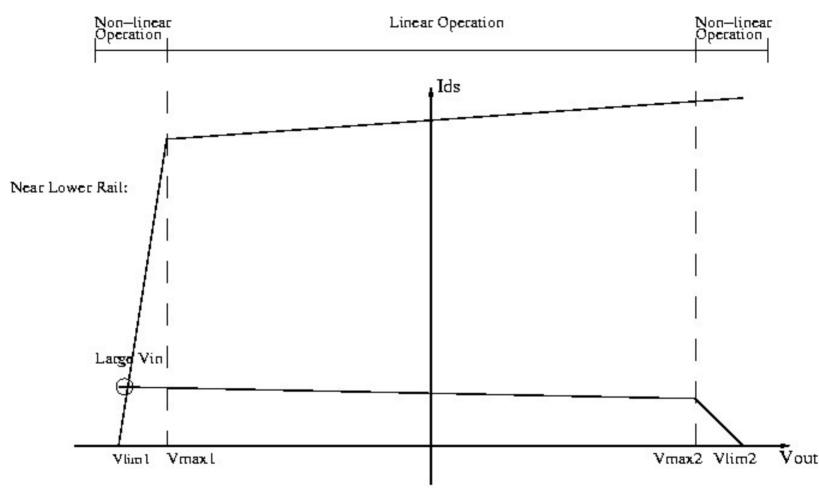

# Large Signal Behavior (cont'd)

$V_{in}$  Increases,  $V_{gs}$  Increases,  $V_{sg}$  Decreases,  $V_{out}$  goes nearer to the lower rail

**BMAS 2007**

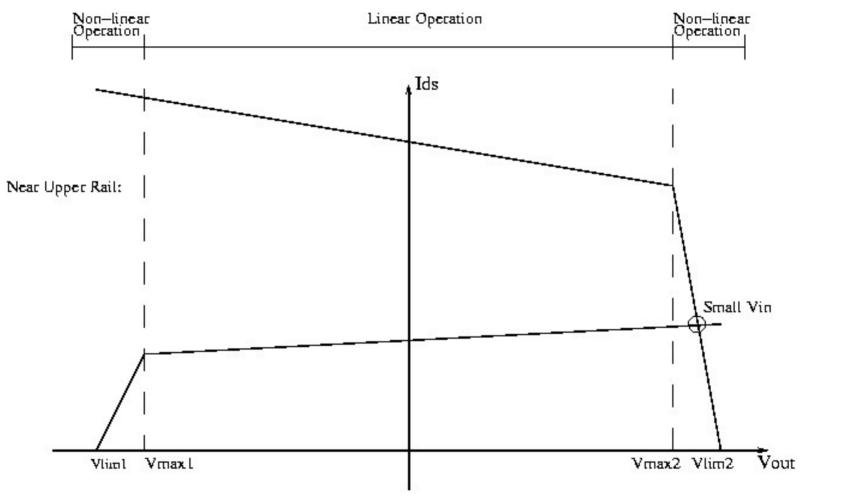

# Large Signal Behavior (cont'd)

$V_{in}$  Decreases,  $V_{as}$  Decreases,  $V_{sa}$  Increases,  $V_{out}$  goes nearer to the upper rail

**BMAS 2007**

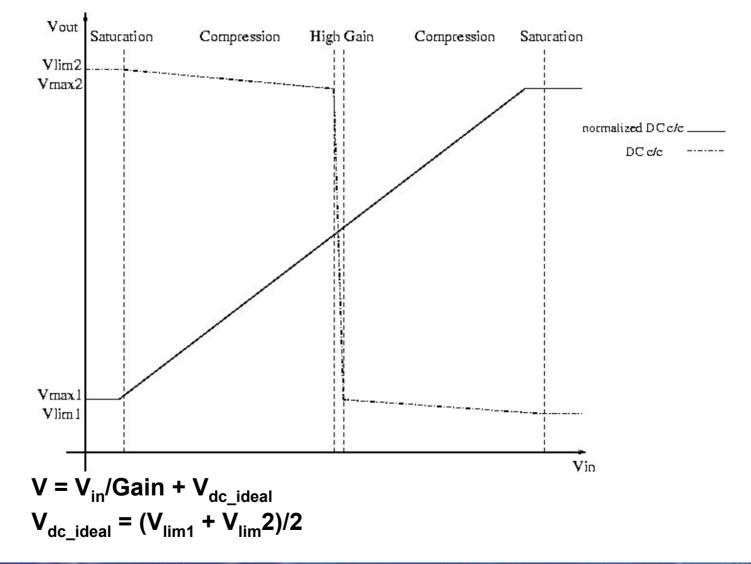

## **DC Characteristics**

**BMAS 2007**

#### **DC Characteristics (cont'd)**

#### Graphiz

**BMAS 2007**

## **Output DC Level**

#### An Output DC level is created by adjusting the values of each device's resistance in saturation.

To calculate each device resistance using the user-defined output resistance and output DC level, we use the following equations :

```

VSD_DC = Vlim2 - Vdc_out - Vdsat_p

```

- VDS\_DC = Vdc\_out Vlim1 Vdsat\_n

- Rsat\_n= rout\*(1.0 + (VDS\_DC)/(VSD\_DC));

- Rsat\_p= Rsat\_n\*(VSD\_DC)/(VDS\_DC);

# **Model Implementation**

- Implemented using VHDL-AMS

- Electrical input and output ports

#### Parameters:

- Limiting voltage

- Output resistance

- Output DC level

- Coding makes use of the language's mixed-signal nature utilizing simulator's mixedsignal kernel for better computational efficiency

entity output\_stage is

generic (Vlim2 : voltage := 10.0 ; -- Upper limiting voltage Vlim1 : voltage := -10.0 ; -- Lower limiting voltage rout : resistance := 1.0e3; -- Output resistance Vdc\_out: voltage := 0.0; -- DC out voltage Vmax1:real := -9.9; -- Lower saturation start Voltage Vmax2:real := 9.9); -- Upper saturation start Voltage port (terminal ain : electrical; -- input terminal terminal aout : electrical); -- output terminal end entity output\_stage; architecture A1 of output\_stage is

V\_in == Vin/gain + Vdc\_ideal;

Vps == Vlim2;

Vns == Vlim1;

if not Vgs'above(0.0) use lds == 0.0;

elsif not vds'above(Vdsat\_n) use lds\*Vdsat\_n == Vgs\*Vds\*Vdsat;

else lds == Vgs\*lambdaN\*(Vds-Vdsat\_n) + Vgs\*(Vdsat); end use;

if not Vsg'above(0.0) use lsd == 0.0;

elsif not vsd'above(Vdsat\_p) use lsd\*Vdsat\_p == Vsg\*Vsd\*Vdsat;

else lsd == Vsg\*lambdaP\*(Vsd-Vdsat\_p) + Vsg\*(Vdsat); end use;

break on Vgs'above(0.0),Vsg'above(0.0);

break on Vds'above(Vdsat\_n),Vsd'above(Vdsat\_p);

end architecture A1;

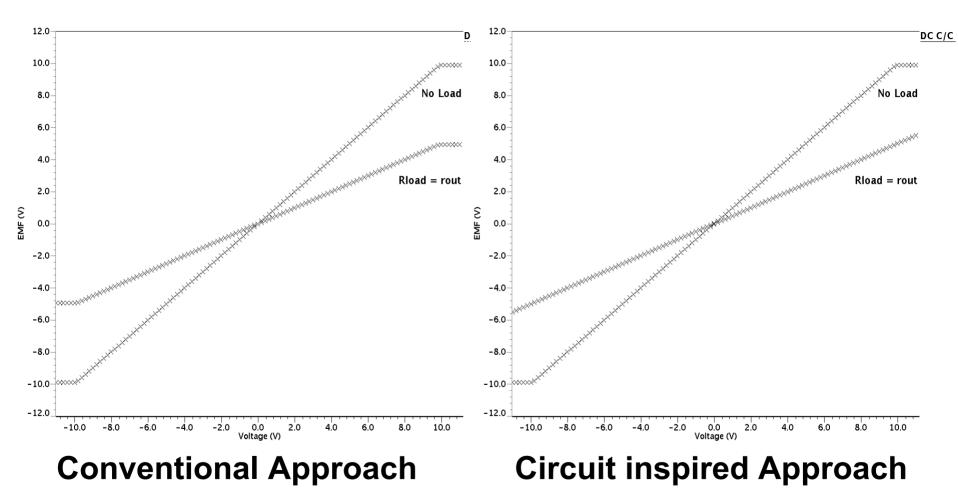

## **Experimental Setup**

Simulations performed using Mentor Graphics, ADVance MS<sup>™</sup> mixed signal simulator.

Loading effect test performed on both the conventional approach model and our proposed model.

A DC analysis is performed while sweeping input Voltage both with and without load.

#### **Experimental Results**

**BMAS 2007**

# **Application**

- Typical application for model would be as an amplifier output stage.

- Simplifies amplifier modeling to input characteristics and core functionality(gain, frequency response).

- In case of balanced differential output, model could be instantiated twice with parameters adjusted to account for differential characteristics.

- Model was used as an opamp output stage and it showed ease of convergence in different feedback configurations.

#### Conclusion

- Modeling analog output behavior should preserve interaction between voltage saturation and output resistance.

- Disregarding such interaction will lead to erroneous results restraining the use of the behavioral model.

- Using abstracted circuit physics successfully captures these inter-related effects.

- Our model provides a solution for modeling output characteristics of an amplifier.

# **Thank You**