# On Accommodating Particular Analog System Models With VHDL

**Gabriel Stefan Popescu** *Technical University of Iasi, Romania* E-mail: gpopescu@ieee.org

## **Simulation Requirements**

Speed - Accuracy Tradeoff

**P**Requirments

PTo take into account performance limiting factors

- < To accurately represent the timing behavior of the modeled hardware

- < The analog behavior of the circuit even for digital circuits.

PTo reduce the costs of the simulation

- < To reduce the simulation time

- < To reduce the memory overhead

PTo manage the simulation of huge simulated systems

## **Interconnection Macromodels**

Interconnections: A Limiting Factor of the Actual Circuit Performances

- PLong line approximations:

- < Precise only for particular topologies.

- P Precise models use complex numeric processing:

- < Convolution,

- < Numerical inversion of the Laplace transform, etc.

- P Reduced order approximations less precise but less numerical intensive:

- < Padé like approximations (AWE, CFH),

- < Krylov subspace approximations (PVL).

## **Simulation of High Speed VLSI Circuits**

The Simulation Approach

- PClassical simulators (SPICE):

- < Low level of model abstraction ÷ high precision.

- < The latency is not exploited ÷ high simulation cost.

P Discrete event simulators (VHDL):

- < High level of model abstraction ÷ low precision.

- < The latency is exploited ÷ low simulation cost.

## **Simulation of High Speed VLSI Circuits**

The Simulation Approach - An Insight Point of View

- PClassical simulators (SPICE):

- < Solves numerically a set of nonlinear differential equations:

- Establishes a discrete equivalent set of equations;

- Solves at discrete moments of time a set of nonlinear equations:

- Solves sets of linear equations computes the terms of a string which eventually converges.

- < The concurrence of the circuit is established by solving a system of equations.

- P Discrete event simulators (VHDL):

- < Solves numerically a set of linear decoupled equations liniarization by abstraction:

- Establishes a discrete-quantized set of equations;

- Solves with respect of time the transitions between to states defined as amplitude vectors

- < The concurrence of the circuit is established using concurrent statements.

## **On Some Event-Driven Aspects of VHDL**

Predefined Discrete Event Features of VHDL

- PThe VHDL grammar proposes two syntactic constructs:

- < Inertial delay (digital devices such as gates, flip-flops, etc.):

- A new input value must persist a minimum amount of time to initiate a change in the state of the component.

- < Transport delay (interconnections):

- Any change of the input signal, regardless of its duration, initiates a change of the state of the device.

- P The transport delay interconnection model assumes some serious limitation:

- < The interconnection has only one tap connected to a driver.

- < The signal is only delayed on the interconnection:

- < Old transactions that are to occur at, or after the time at which the earliest new transaction is projected are deleted from the event queue:

- The energy of any signal can be vanished without any impact on the system behavior.

## **The Proposed Approach**

**Features of the Model**

- PThe targeted interaction between the macromodel and VHDL:

- < Avoid modifications in the VHDL standard,

- < Avoid limitations imposed to the modeled system.

- PThe interconnection macromodel is implemented as an *entity* that must satisfy two essential conditions:

- < The macromodel must be able to be activated by the input signals:

- Initial activation a consequence of the activity of one or more drivers connected at the interconnection taps.

- < The macromodel must have a mechanism to auto activate until it reaches a temporary steady state corresponding to the input and output signal's state:</p>

- Events are necessary to update the state of the interconnection during the propagation of the signals.

## **The Proposed Approach**

The model development

- PThe definition of the events and their transactions for the analog system:

- < Discrete amplitude;

- < Discrete time.

- PIntermediate layer translation to the VHDL's events and their transactions:

- < The evolution of the system with constant imput values;

- < The synchronization due to the modifications of the input values.

- **PImplementation for VHDL**

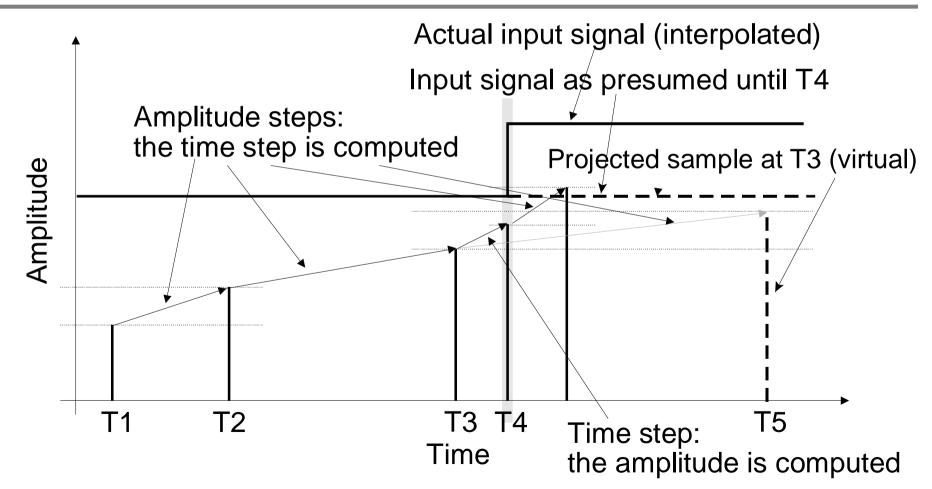

### **Example of event - transaction**

PAt the moment T4 an event occures on the input signal ÷ synchronisation.

## The analog system representation

PThe hybrid representation for the N-port which represents the modeled system the in the frequency domain:

Y(s) = H(s)X(s)

$$Y_{k}(s) \neq \begin{cases} I_{k}(s) & \text{when } X_{k}(s) \neq V_{k}(s) \\ V_{k}(s) & \text{when } X_{k}(s) \neq I_{k}(s) \end{cases} k^{-1} 1, \ddot{y}, n$$

$$H_{pq} = K^{pq} + \frac{m_{1}}{j} \frac{k_{i}^{pq}}{(s+p_{i})^{j_{i}^{-1}}} + \frac{m_{1}+m_{2}}{j} \left(\frac{k_{i}^{pq}}{(s+p_{i})^{j_{i}^{-2}}} + \frac{k^{(pq)}_{i}}{(s+p_{i})^{j_{i}^{-2}}}\right)$$

PTo accomplish equation decoupling - enabling milti rating integration:

$$Y_{p} = \sum_{q=1}^{n} Y_{pq}(s) = \sum_{q=1}^{n} \sum_{i=1}^{1+m_{1}+m_{2}} Y_{pqi}(s)$$

## **Real Poles**

#### PFor the term:

$$Y_{pqi}(s) = \frac{k_i^{pq}}{s + p_i} X_q(s)$$

PThe time domain equation is:

$$\begin{cases} \frac{d}{dt} y_{pqi} = \& p_i y_{pqi} + k_i^{pq} x_q \\ y(t_0) = y_0 \end{cases}$$

PAmplitude step: < Evolution

$$t_{n+1} - t_n = \begin{bmatrix} l & l \\ y_{pq \ i \ n+1} & - \mathbf{j} \\ \mathbf{j}_{j=0} & a_j y_{pq \ i \ n-j} \end{bmatrix} @ \begin{bmatrix} l & b_j - p_i y_{pq \ i \ n-j} + k_i^{pq} x_{n-j} \\ \mathbf{j}_{j=-1} & b_j - p_i y_{pq \ i \ n-j} \end{bmatrix} ^{-1}$$

#### PTime step:

< Synchronisation

$$y_{pq\,i\,n+1} = \begin{bmatrix} l & l \\ \mathbf{j}_{j=0} & a_j y_{pq\,i\,n-j} + f_{n+1} - t_n \mathbf{j}_{j=0} & b_j - p_i y_{pq\,i\,n-j} + k_i^{pq} x_{n-j} \mathbf{i} + f_{n+1} - t_n \mathbf{i}_{n-1} & b_{-1} k_i^{pq} x_{n+1} \end{bmatrix} @$$

$$@ 1 + f_{n+1} - f_n \mathbf{i}_{n-1} & b_{-1} p_i \mathbf{i}_{n-1}$$

## **Complex Poles**

PFor the term:

$$Y_{pqi}(s) = \left(\frac{k_i^{pq}}{s + p_i} + \frac{k_i^{(pq)}}{s + p_i^{(pq)}}\right) X_q(s)$$

PTime step:

< Synchronisation

$$\begin{cases} \frac{d}{dt} y_{pq\,i\,1R} = \& p_{i\,R} y_{pq\,i\,1R} + p_{i\,I} y_{pq\,i\,1I} + k_{i\,R}^{pq} x_q \\ \frac{d}{dt} y_{pq\,i\,1I} = \& p_{i\,I} y_{pq\,i\,1R} - p_{i\,R} y_{pq\,i\,1I} + k_{i\,I}^{pq} x_q \\ y_{pq\,i\,1R} (t_0) = y_{pq\,i\,1R\,0} \\ y_{pq\,i\,1I} (t_0) = y_{pq\,i\,1I\,0} \\ y_{pq\,i} = 2 y_{pq\,i\,1R} \end{cases}$$

## **Amplitude discretization**

- PToo many steps reduce the simulation efficiency,

- PToo few affect the accuracy of the simulation results.

- PAssumptions.

- < Uniform discretization

- < The local steady state is given by the value zero of the derivative of the output when the input value is constant

- < M is the number of amplitude steps per input amplitude unit

PA real pole:

$$\mathbf{y}_{pq\,i} = \left\{ \frac{k_i^{\,pq}}{M\,p_i} \right\}$$

PA pair of complex poles:

$$) y_{pq\,i\,1R} = \begin{cases} \frac{k_{i\,R} p_{i\,R} + k_{i\,I} p_{i\,I}}{M_{0} p_{i\,R}^{2} + p_{i\,I_{\bullet}}^{2}} \end{cases}; \ ) y_{pq\,i\,1I} = \begin{cases} \frac{k_{i\,R} p_{i\,R} - k_{i\,I} p_{i\,I}}{M_{0} p_{i\,R}^{2} + p_{i\,I_{\bullet}}^{2}} \end{cases}$$

## **Experimental results**

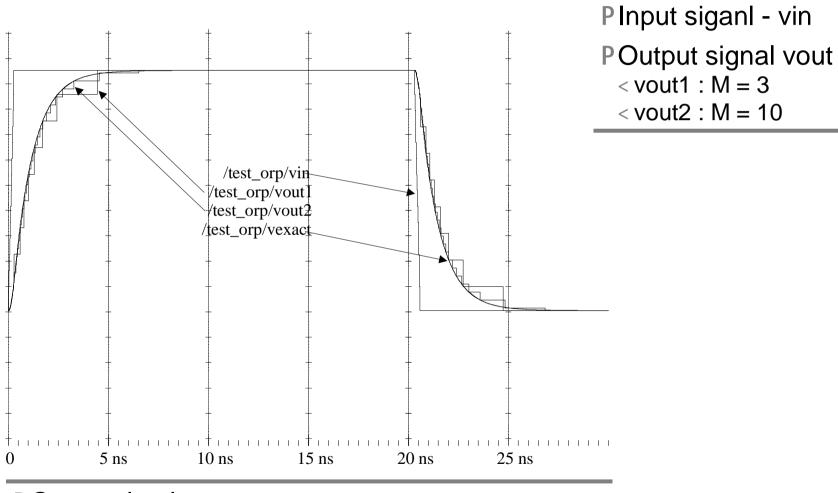

POne real pole

PInput siganl - vin POutput signal vout < vout1 : M = 3 < vout2 : M = 10

BMAS 2000

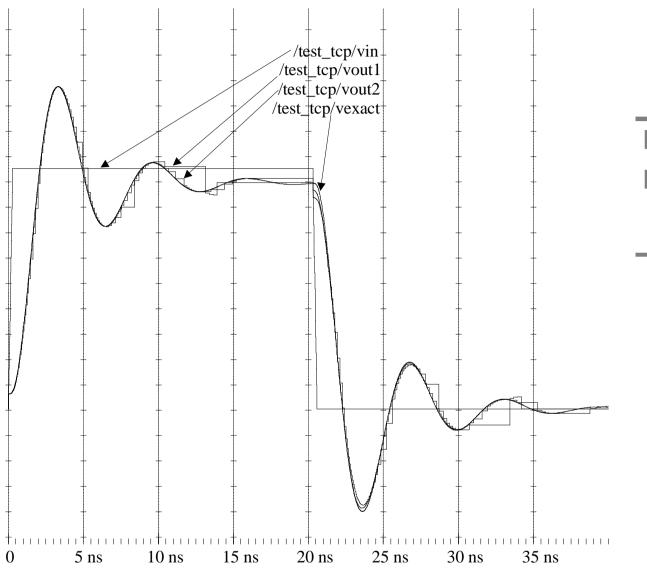

#### PComplex poles

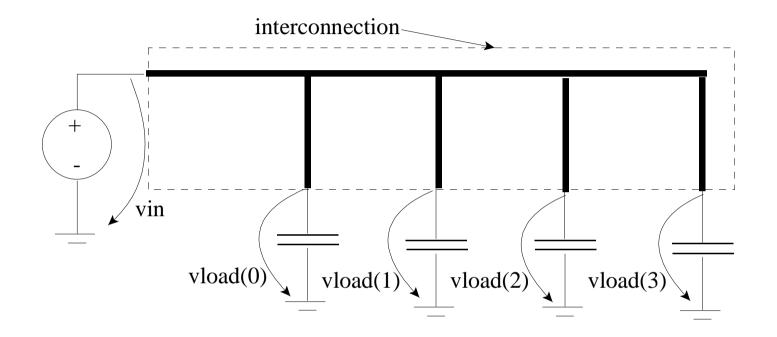

#### PThe topology of a test interconnection.

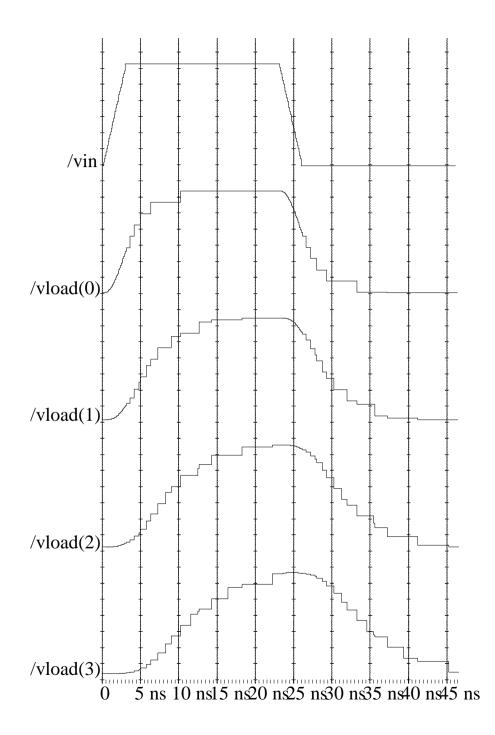

P Simulation results for a interconnection modeled using real poles

BMAS 2000

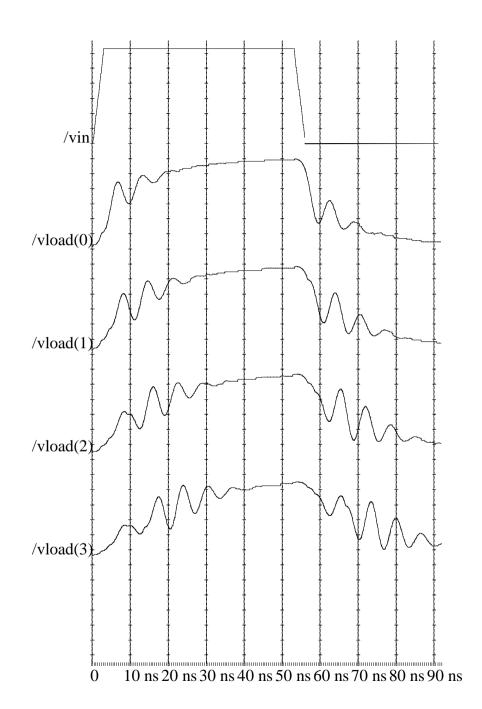

P Simulation results for a interconnection modeled using both real and complex poles

## Conclusions

- PThe paper discusses the development of a VHDL analog system modeling approach with applications in interconnections' modeling.

- PThe method is based on a multi rate integration approach derived from an implicit integration algorithm exhibiting:

- < Latency exploitation;

- < Superior stability properties of implicit integration methods.

- PThe modeling process uses available VHDL constructions.

- P An extra layer of the model adapt the set of events and their transaction imposed by the analog stage to the discrete event approach used by the discrete event simulator. In this layer tow kind of iterations are used:

- < Amplitude step evolution

- < Time step synchronization.

- P The obtained modeling solution is able to represent analog behavior including crosstalk and non monotonic transitions.

- P It is usable only into a particular simulation scenario mainly when the analog stage of the circuit is represented by nonideal interconnections.