Electronics & Computer Science University of Southampton

#### Behavioural Simulation and Synthesis of Biological Neuron Systems using VHDL

J.A. Bailey<sup>1</sup>, P.R. Wilson<sup>1</sup>, A.D. Brown<sup>1</sup> and J.E. Chad<sup>2</sup> School of Electronics and Computer Science<sup>1</sup> & School of Biological Sciences<sup>2</sup> University of Southampton, SO17 1BJ, U.K.

- The Nervous System

- VHDL Neuron Model

- VHDL Neuron Network Model

- Synthesis

- Biologists & Engineers

- Investigate Neuron Structures

- Biological experiments

- Live Tissue

- Can't Establish Connectivity

- Behavioural Modelling

- Simulate behaviour

- Determine network characteristics

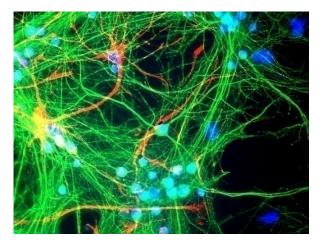

Stained Rat Cortical Neurons [1]

### **Motivation**

- → Biologically realistic simulation

- Efficient Models

- Reduce run time

- Hardware acceleration

- Real Time Simulation

- Virtual Animal/Nervous System

- Reusable Libraries

- Easily configurable

- → The Nervous System

- VHDL Neuron Model

- VHDL Neuron Network Model

- → Synthesis

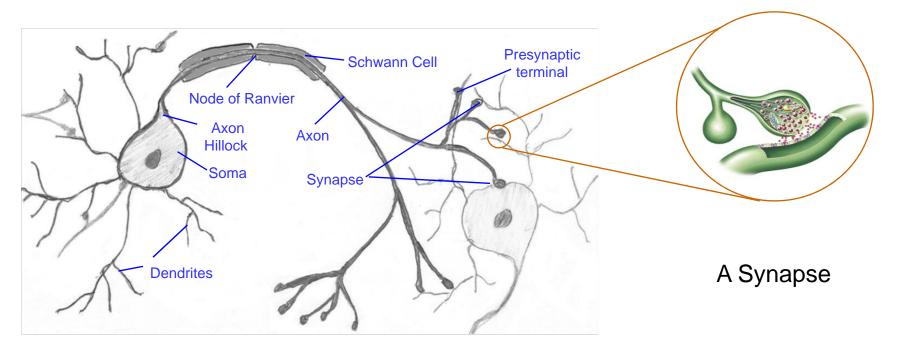

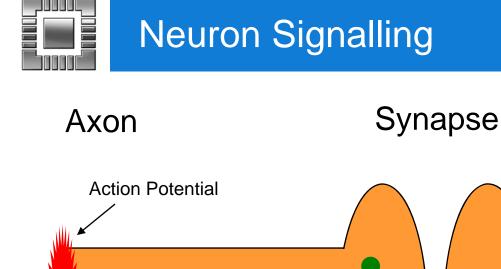

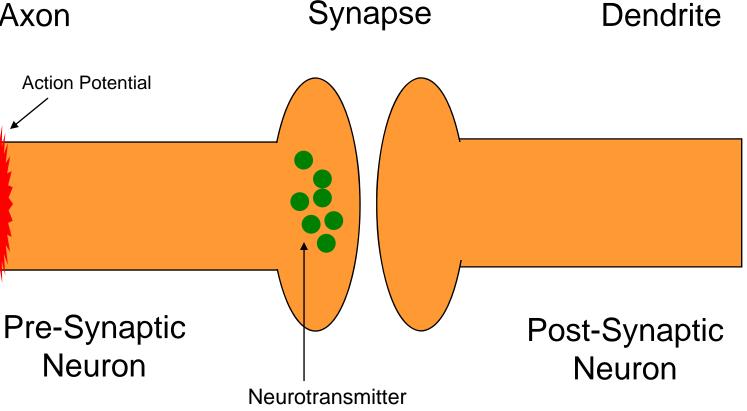

## A Typical Neuron

A Typical Neuron

- The Nervous System

- → VHDL Neuron Model

- VHDL Neuron Network Model

- → Synthesis

## History of the VHDL Model

#### Cell Automata Model

→ Enric Claverol, 2000

Claverol, E.T. Brown, A.D. Chad, J.E., "Message Based Event Driven Model (MBED) A largescale simulation of the piriform cortex by a cell automaton-based network model", IEEE Trans. Biomedical Engineering, Vol. 49(9), pp 921-935, Sept 2002.

- System C Neuron Model

- → Sankalp Modi, BMAS, 2004

- VHDL Biologically realistic neuron model

- → Julian Bailey, BMAS 2007

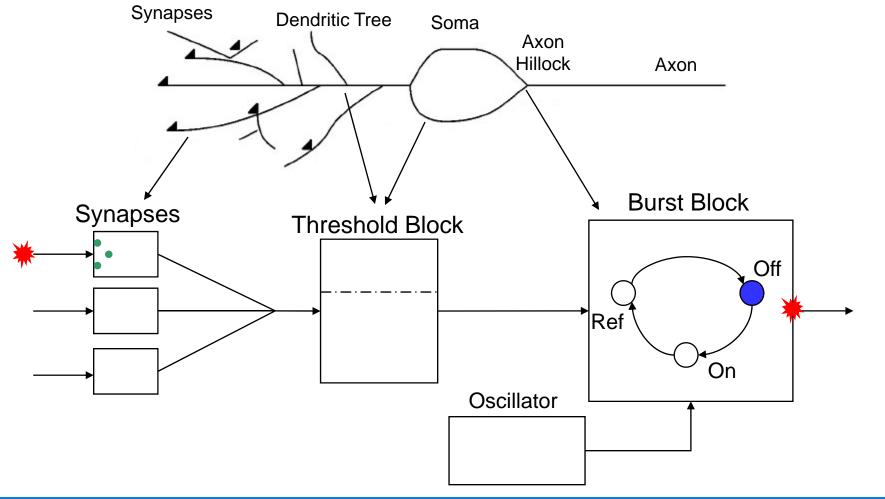

## Model Overview

### More Model Details

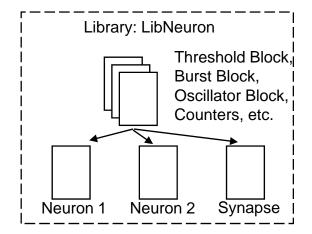

- Neuron Library LibNeuron

- Contains all Sub Components

- Three top level entities

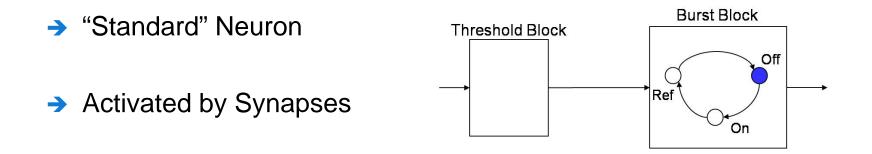

- Neuron 1

- Neuron 2 (Oscillator Activated Neuron)

- Synapse

- Each Configurable using Generics

So

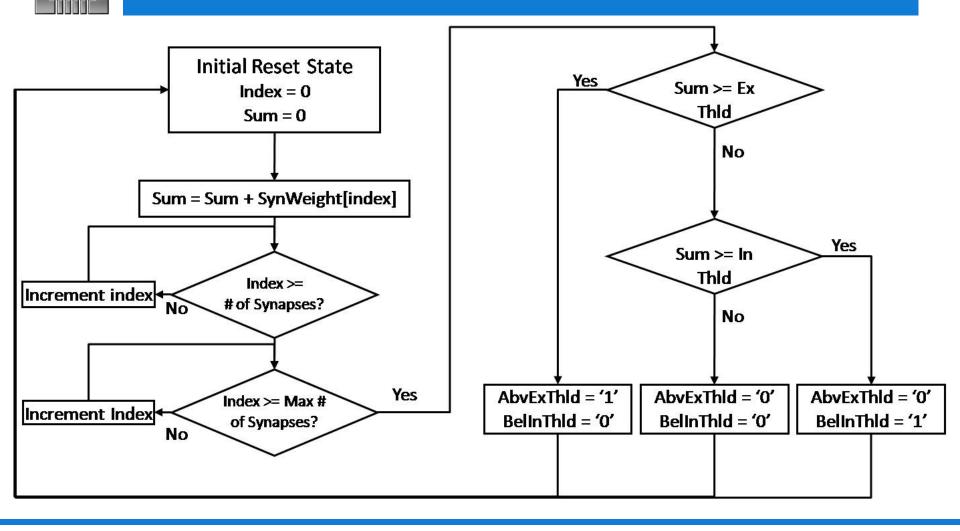

## Sub Component – Threshold Block

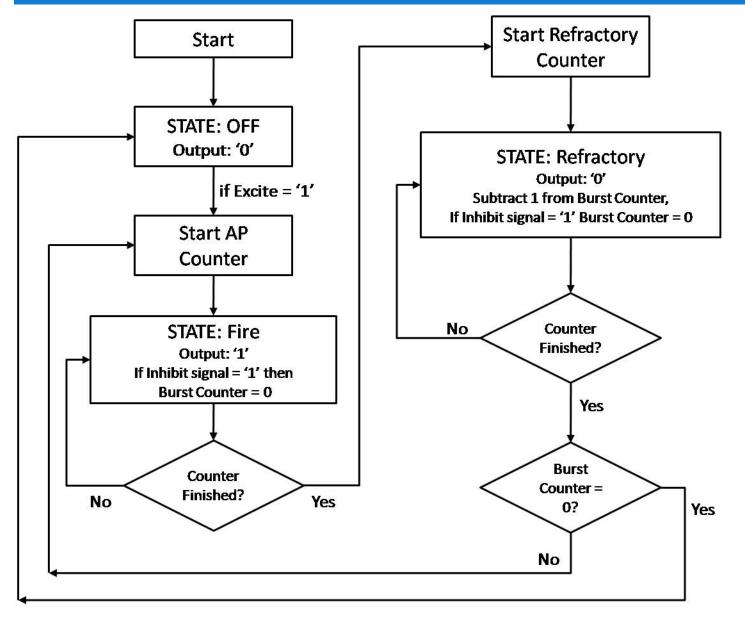

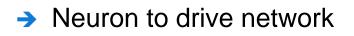

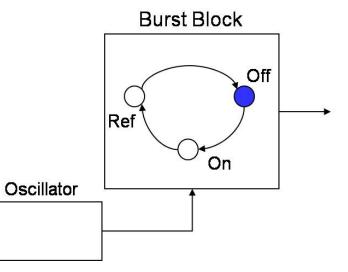

### Sub Component – Burst Block

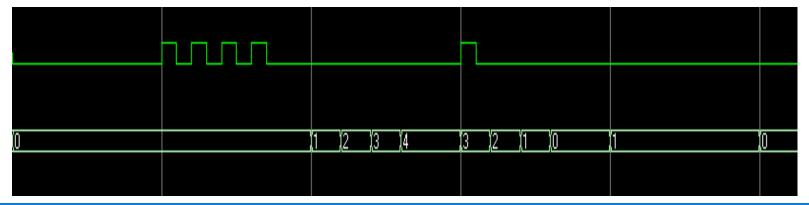

Example Parameters:- Threshold 3, AP Time 1 ms, Ref. Time 2 ms, Burst 5.

| ) | 3 |  | 0 |  |  |  |  |  |

|---|---|--|---|--|--|--|--|--|

|   |   |  |   |  |  |  |  |  |

| ) |   |  |   |  |  |  |  |  |

|   |   |  |   |  |  |  |  |  |

|   |   |  |   |  |  |  |  |  |

|   |   |  |   |  |  |  |  |  |

Activated periodically by oscillator

Example Parameters:- Period 16 ms, Phase 2ms, AP Time 1 ms, Ref. Time 2 ms, Burst 3.

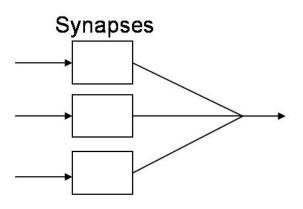

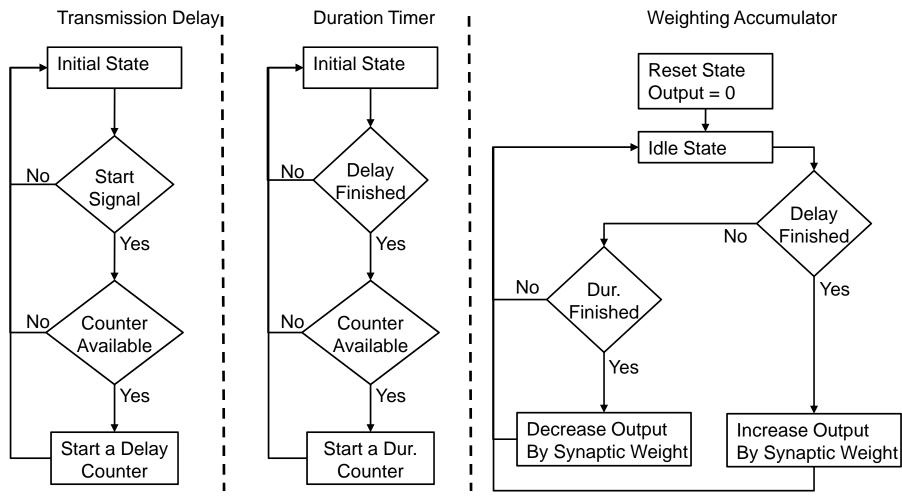

- Connect Neurons

- Model Delays & Activation Duration

- Can be activated once already active

Example Parameters:- Delay 1ms, Duration 1ms, Weighting 1.

Sou

UNIVERSITY OF

## Inside the Synapse

- The Nervous System

- VHDL Neuron Model

- → VHDL Neuron Network Model

- → Synthesis

## **Model Verification**

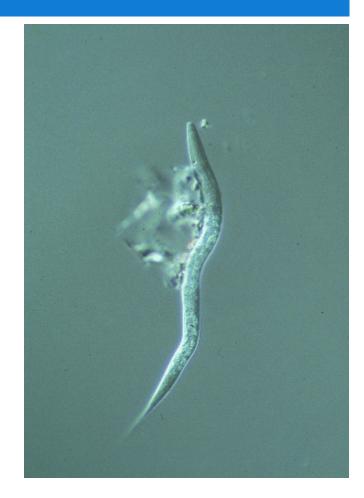

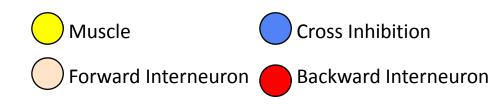

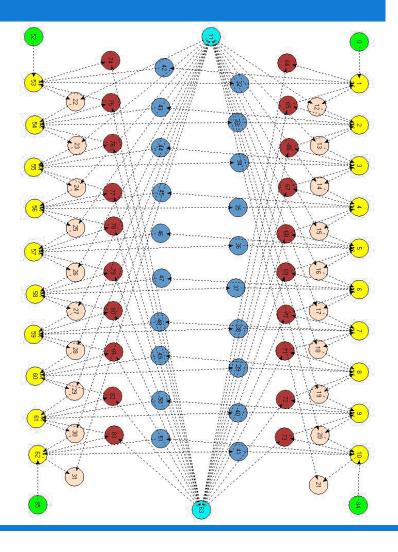

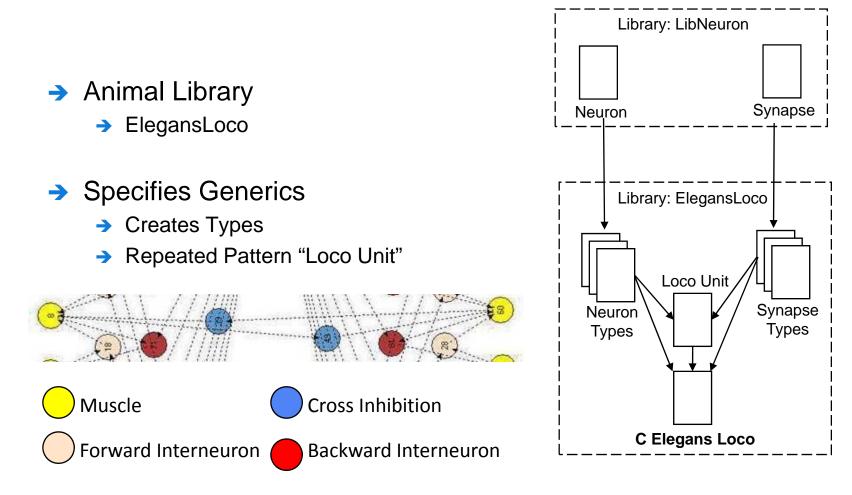

- → Nematode, C Elegans

- → 302 Neurons

- Extensively studied

- Connections partially known

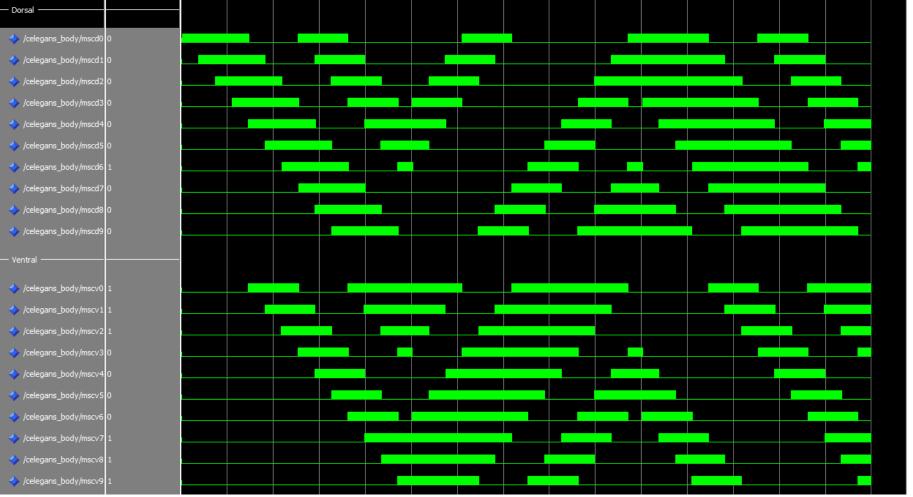

## LibElegans VHDL Library

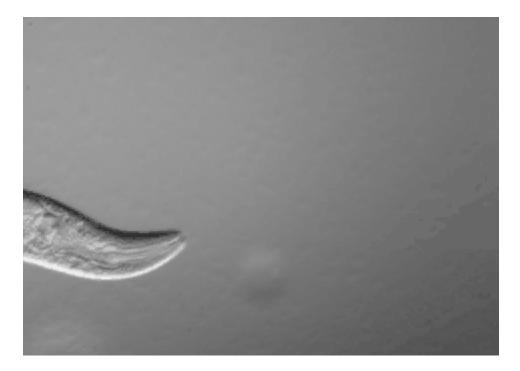

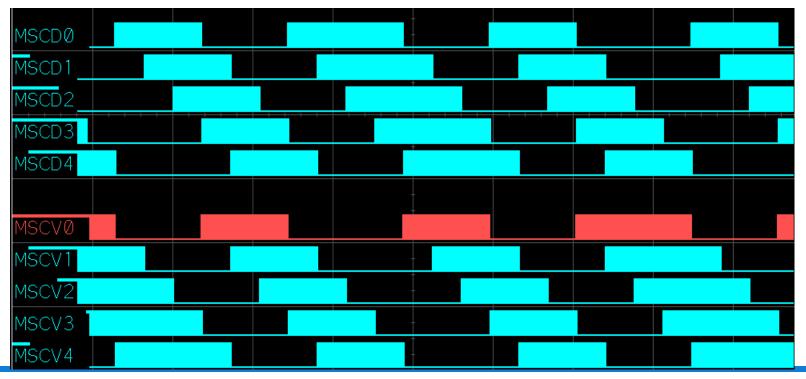

## **Simulation Results**

- The Nervous System

- VHDL Neuron Model

- VHDL Neuron Network Model

- → Synthesis

## Synthesis

- Previous work

- → C Elegans Design Size (200k FG, 85k DFF's)

- Optimisation

- 2 Types of Neuron

- User Definable Length Counters

- Up Counters only

- Disable Pins on all blocks

- Design fits on many more devices

- → 60,506 FG's & 48,891 DFF's

- Hardware acceleration

#### Stained Hippocampal Neuron [1]

## Synthesis Example

#### → A section of C Elegans (Mini Elegans)

- → 33 Neurons, 50 Synapses

- Only goes forwards

### Hardware Acceleration

- Traditional Simulations

- ➔ Hours -> Days

- → Example: Mini Elegans (6 Sec) 3 hours 20 mins

- → Example: C Elegans (15 Sec) 32 hours 12 mins

- ➔ In Hardware

- → Real-Time

- → Example: Mini Elegans (6 Sec) 6 Seconds! (2000x Faster)

- → Near Future : C Elegans (15 sec) 15 Seconds! (7728x Faster)

- → However...

- Limited by Current FPGA Technology

- Large Scale Multi-Processor Hardware Simulation Frameworks

- → Spinnaker Univ. Southampton, UK & Univ. Manchester, UK

- Synthesizable Neuron Library

- Post-Synthesis Verification

- Compared against previous work

- → C Elegans

- Post Synthesis design

- Reasonably sized

- Download onto FPGA

- Hardware acceleration

- → Virtual Animal/Nervous System on FPGA!!!

## Any Questions ?