# Improved Phase Noise Model for Ultra Wideband VCO

#### Li Ke Reuben Wilcock Peter Wilson

- Research motivation

- Improved phase noise model

- Simulation results

- Measurement results

- Conclusions

# **Research motivation**

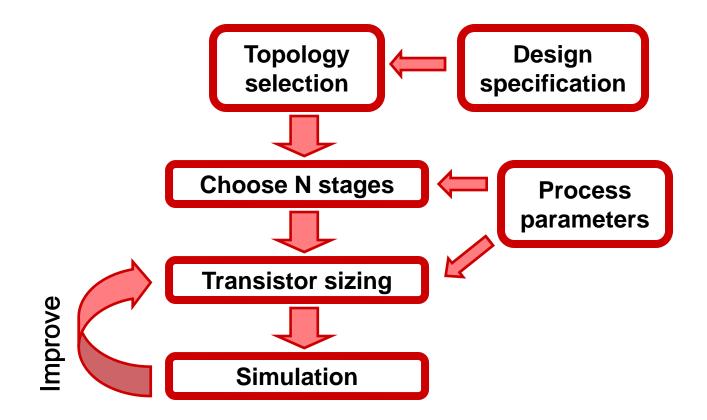

### Typical VCO design flow

- Topology and number of stages chosen from experience

- Starting point and simulation led improvement

# **Research motivation**

### Voltage controlled oscillator design challenges

- Lack of detailed transistor sizing guidelines which relate high level specifications to W and Ls.

- Small signal model (Barkhausen Criteria) only holds valid for linear operation.

- Jitter/Phase noise performance is an important specification in VCO design.

- Phase noise and jitter simulations in leading simulators (e.g. SpectreRF) are extremely time consuming.

# Requirement for a phase noise targeted transistor sizing model.

## **Research motivation**

- Previous work has considered a number of factors when modelling VCO phase noise

- Process parameters

- Power supply

- Topology

- Transistor dimensions

- Oscillation frequency

#### However:

# No one has considered the effect of frequency tuning on phase noise.

- Research motivation

- Improved phase noise model

- Simulation results

- Measurement results

- Conclusions

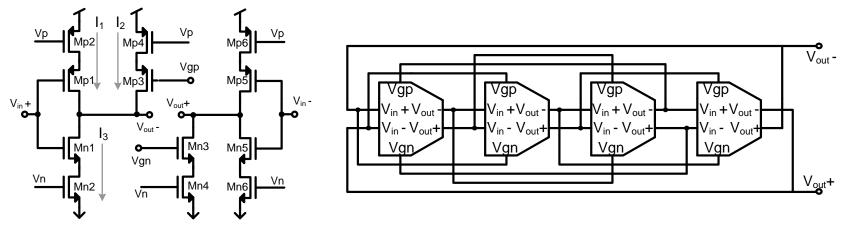

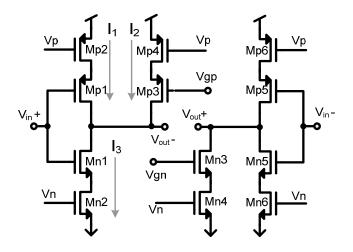

The proposed model is based on the new dual inverter delay cell which has 10 octave tuning range.[1]

Previous design guidelines for this cell simply ensure that I<sub>1</sub> + I<sub>2</sub> = I<sub>3</sub>

[1] Li Ke, Reuben Wilcock, Peter Wilson "Improved 6.7GHz CMOS VCO Delay Cell With Up To Seven Octave Tuning Range ", *Proceedings of IEEE ISCAS*, May 2008

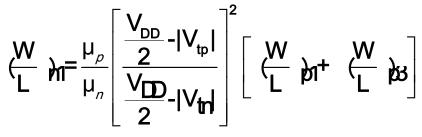

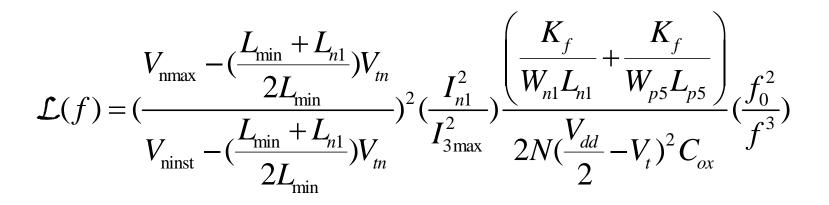

For a phase noise orientated design approach, existing models can be expressed as[2]:

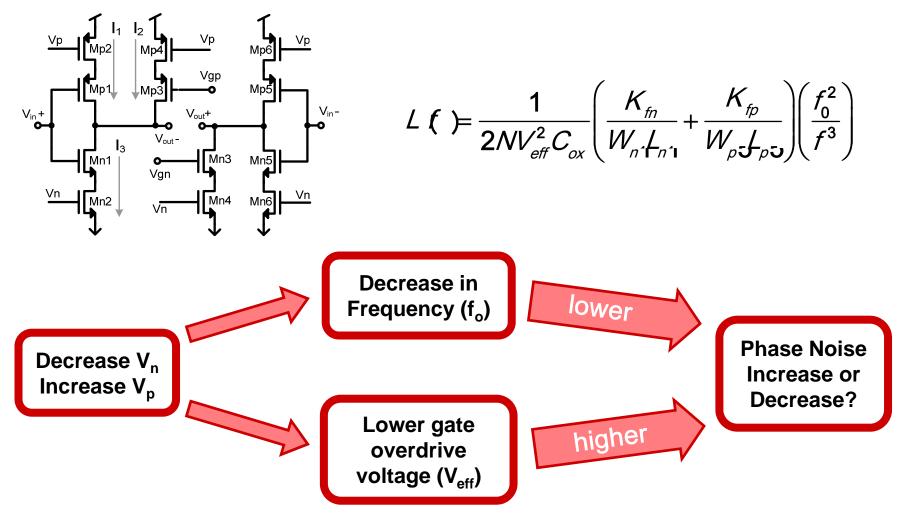

$$L(f) = \frac{1}{2NV_{eff}^2 C_{ox}} \left( \frac{K_{fn}}{W_{n1}L_{n1}} + \frac{K_{fp}}{W_{p5}L_{p5}} \right) \left( \frac{f_0^2}{f^3} \right)$$

#### Takes account of:

- Oscillation frequency: f<sub>0</sub>

- Process parameter: K<sub>fn</sub>,K<sub>fp</sub>, C<sub>ox</sub>

- Transistor dimensions: W<sub>n1</sub>, L<sub>n1</sub>, W<sub>p5</sub>, L<sub>p5</sub>

- Topology: N

(Generally accepted that 1/f noise dominates the spectrum up to a few MHz)

[2] Sohrab Samadian, Michael M. Green, "Phase Noise in Dual Inverter-Based CMOS Ring Oscillator", *Proceddings of IEEE ISCAS*, May 2006

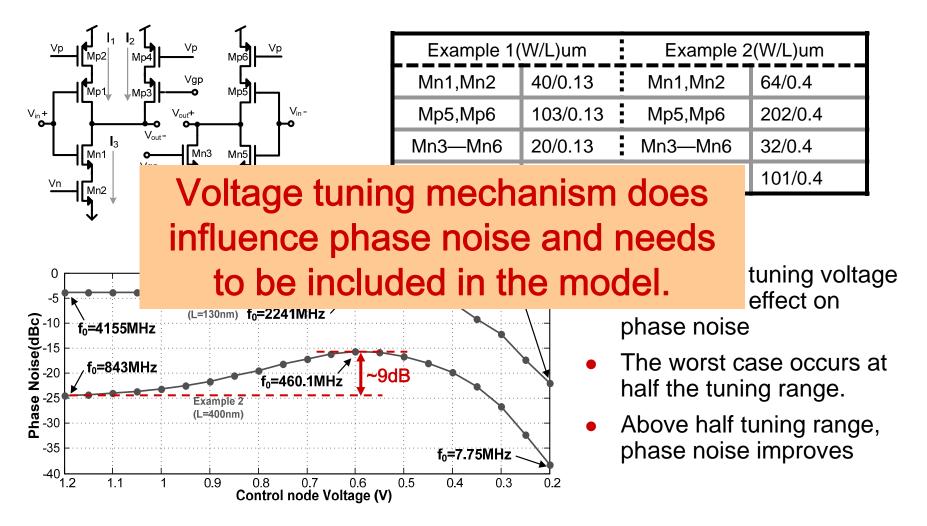

What happens when the tuning voltage changes?

Post layout simulation results (SpectreRF-PSS-Pnoise)

Including the voltage tuning mechanism in the model: part 1

- We introduce the terms instantaneous current  $I_{inst}$  and maximum achievable current  $I_{max}$ .

- $I_{inst}$  corresponds to the  $V_{ninst}$  and  $I_{max}$  correspond to  $V_{nmax}$  which is the maximum achievable control node voltage (normally equal to  $V_{dd}$ ).

- Use the  $I_3$  as an example, from the simulation, the ratio of these two values can be expressed as:

$$P = \frac{I_{3 \max}}{I_{3 inst}} = \frac{V_{n\max} - ((L_{\min} + L_{n1}) / 2L_{\min})V_{tn}}{V_{ninst} - ((L_{\min} + L_{n1}) / 2L_{\min})V_{tn}}$$

• L<sub>min</sub> is the minimum allowable transistor length defined by process

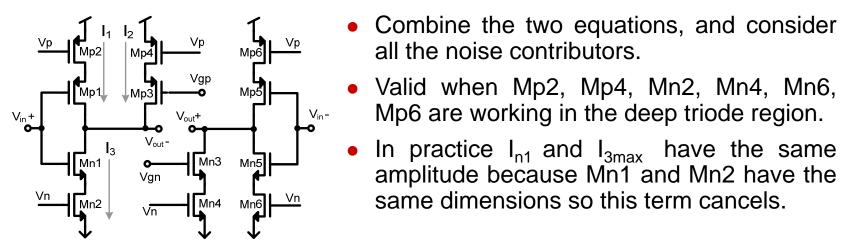

Including the voltage tuning mechanism in the model: part 3

- Combine the two equations, and consider

- Research motivation

- Improved phase noise model

- Simulation results

- Measurement results

- Conclusions

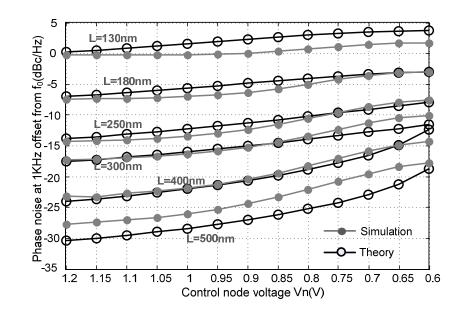

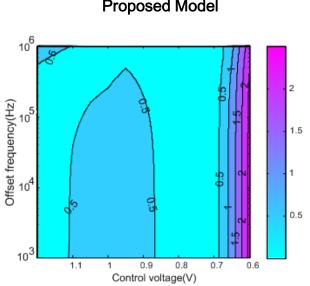

#### The results show good comparison with simulation.

• Previous model only valid at highest frequency

#### Further model validation

- Transistor lengths from 120nm to 500nm

- Phase noise simulations

- Error is less than 3dB over 0.6-1.2V tuning range

|                    | Transistor Dimensions: |                 | Performance at Vn=1.2V        |                                                               | Performance at Vn=0.6V        |                                                               |

|--------------------|------------------------|-----------------|-------------------------------|---------------------------------------------------------------|-------------------------------|---------------------------------------------------------------|

| Example<br>number: | Wp5/Lp5<br>(um)        | Wn1/Ln1<br>(um) | Oscillation<br>frequency(MHz) | Phase Noise at<br>1KHz offset from<br>f <sub>0</sub> (dBc/Hz) | Oscillation<br>frequency(MHz) | Phase Noise at<br>1KHz offset from<br>f <sub>0</sub> (dBc/Hz) |

| 1                  | 103/0.13               | 40/0.13         | 6521                          | -0.237                                                        | 3592                          | 1.645                                                         |

| 2                  | 132/0.18               | 48/0.18         | 3934                          | -7.4                                                          | 2144                          | -2.94                                                         |

| 3                  | 168/0.25               | 56/0.25         | 2301                          | -14.25                                                        | 1258                          | -7.53                                                         |

| 4                  | 153/0.3                | 50/0.3          | 1695                          | -17.27                                                        | 928.8                         | -10.03                                                        |

| 5                  | 202/0.4                | 64/0.4          | 1026                          | -23.21                                                        | 566                           | -14.32                                                        |

| 6                  | 260/0.5                | 80/0.5          | 687.5                         | -27.72                                                        | 380.5                         | -17.77                                                        |

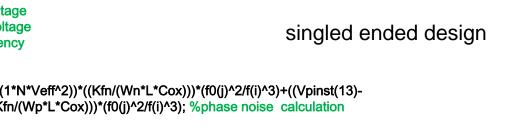

#### Verification of model for single ended designs

```

eox = 3.45e-11; % permittivity of the silicon oxide F/m

tox = 2.462e-9; %gateoxide thickness m

Cox = eox/tox; % gate oxide capacitance per unit areaf/m^2

Mp6

Kfp = 1e-24; % Flcker noise coefficient

Kfn = 1e-24; % Flcker noise coefficient

Vt=0.25; % Threshold voltage for the process

<sup>•</sup> Mp5

Vdd=1.2; % Vdd

Veff= (Vdd/2-Vt) ;

f= 1e3:1e3:1e6; % offset frequency with 1KHz step size

Wp=202e-6; % PMOS width

Mn1

Wn=64e-6; % NMOS width

L=400e-9; %Transistor length

N=5; % number of delay stages

h Mn2

p=(130+400)/(2*130); % Coefficient

Vninst=0.6:0.05:1.2; %Vn instant control voltage

Vpinst=1.2:-0.05:0.6; %Vp instant control voltage

f0=364e6:26.8e6:686e6; %oscillation frequency

for i =1:length(f0)

for i=1:length(f)

Lf2(i) = ((Vdd-p*Vt)/(Vninst(j)-p*Vt))^2*(1/(1*N*Veff^2))*((Kfn/(Wn*L*Cox)))*(f0(j)^2/f(i)^3)+((Vpinst(13)-

p*Vt)/(Vpinst(j)-p*Vt))^2*(1/(1*N*Veff^2))*((Kfn/(Wp*L*Cox)))*(f0(j)^2/f(i)^3); %phase noise calculation

logf2(i)=10*log10(Lf2(i));

end

logfcaltotal(j,:)=logf2;

end

load phasenoise simulation %(Load the Simulation results from cadence spectreRF)

logfsimulation=phasenoise_simulation';

```

error=abs(logfsimulation-logfcaltotal); % Calculate the abslute error between the Theory and simulation

• Vout

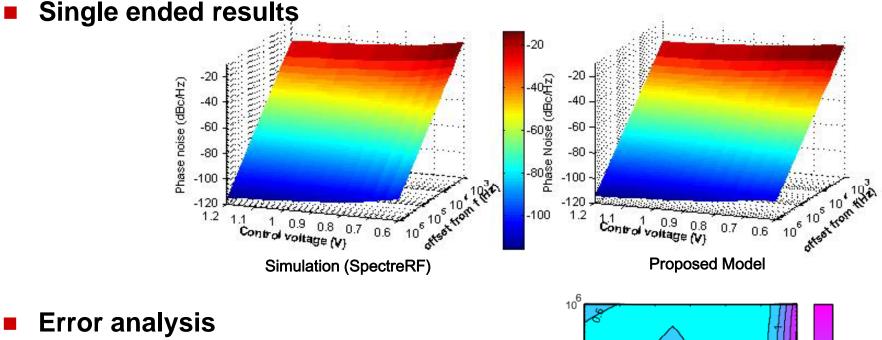

- From the surface plots, the maximum error is less than 3 dB.

- The proposed phase noise model holds valid for single ended oscillators as well.

- Research motivation

- Improved phase noise model

- Simulation results

- Measurement results

- Conclusions

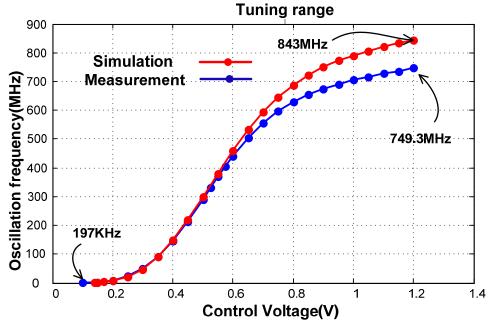

#### Tuning summary

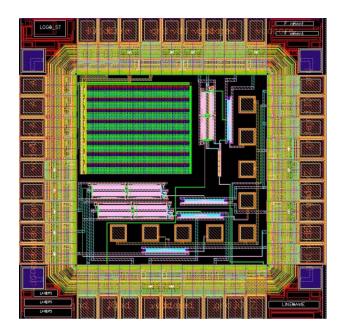

- One design example has been fabricated on a 120nm process

- Process model inaccuracies account for reduction in measured frequency.

| Specification:                   | Design Example 1 |  |

|----------------------------------|------------------|--|

| Supply voltage                   | 1.2V             |  |

| Process                          | 120nm            |  |

| Frequency range<br>(measurement) | 197KHz-749MHz    |  |

| Size                             | 249μm×57μm       |  |

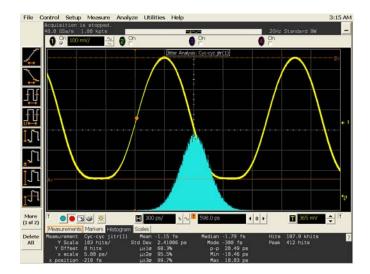

#### Phase Noise measurements

L(f)=-87dBc@100KHzoffset from 749MHz

L(f)=-77.9dBc@100KHzoffset from 477MHz

#### Tuning voltage effect on phase noise

- Results at 100KHz offset from carrier

- Measured results compare well with improved model

| Control Voltage<br>Vninst(V) | Oscillation<br>frequency<br>f <sub>0</sub> (MHz) | Theoretical<br>Phase Noise<br>(dBC/Hz) | Measurement<br>Phase Noise<br>(dBC/Hz) |

|------------------------------|--------------------------------------------------|----------------------------------------|----------------------------------------|

| 1.2                          | 749                                              | -86.775                                | -87.04                                 |

| 0.97                         | 688.1                                            | -83.9935                               | -84.45                                 |

| 0.74                         | 573.2                                            | -79.5658                               | -79.45                                 |

| 0.65                         | 476.6                                            | -76.8662                               | 77.85                                  |

- Research motivation

- Improved phase noise model

- Simulation results

- Measurement results

- Conclusions

# Conclusions

- We have demonstrated that VCO tuning voltage does has an impact on phase noise performance.

- Existing phase noise models for differential delay cells have been extended to include this factor.

- The improved phase noise model has been shown to hold true over a large design space.

- Silicon prototype results indicate that the model can accurately predict the phase noise results.

- The proposed model has been built into a matlab model to reduce the design time of delay cell based VCOs.

## **Questions?**

email: kl05r@ecs.soton.ac.uk

#### Jitter summary

| Specification:     | Design Example 2 |     |         |                  |  |  |

|--------------------|------------------|-----|---------|------------------|--|--|

| Supply voltage     | 1.2V             |     |         |                  |  |  |

| Process            | 0.13µm(St120nm)  |     |         |                  |  |  |

| Frequency<br>range | 197KHz-749MHz    |     |         |                  |  |  |

| Size               | 249μm×57μm       |     |         |                  |  |  |

|                    | 749MHz           | RMS | 2.41ps  | 0.18% of period  |  |  |

|                    |                  | P-P | 20.49ps | 1.5% of period   |  |  |

| Jitter             | 505MHz           | RMS | 1.95ps  | 0.099% of period |  |  |

| (Measurement)      |                  | P-P | 16.96ps | 0.84% of period  |  |  |

|                    | 48.1MHz          | RMS | 8.75ps  | 0.042% of period |  |  |

|                    |                  | P-P | 84.26ps | 0.4% of period   |  |  |

|                    | 749MHz           |     | ≈24mW   |                  |  |  |

| Power              | 505MHz           |     | ≈15.6mW |                  |  |  |

|                    | 48.1MHz          |     | ≈2.98mW |                  |  |  |