### BER and Power Consumption Estimation Based on Hierarchical Modeling of a 2.4 GHz Power Amplifier

*Lucas Alves da Silva, William Tatinian, Gilles Jacquemod LEAT - UMR CNRS UNS 6071*

IEEE Behavioral Modeling and Simulation Conference September 23<sup>rd</sup> and 24<sup>th</sup>, 2010 - Session 2.2, 1:30 - 2:30 PM

ANTENNES ET TELECOMMUNICATIONS

- Introduction

- Power estimation framework

- Hierarchical modeling

- Conclusions

### Introduction

ENNES ET TELECOMMUNICATIONS

- Power consumption remains as one of the major issues in micro and nanoelectronics industry

- Integration leads to the increase in system complexity

- SoC can include several processing units, DSP, memories, sensors, RF transceivers, MEMS, etc

- Providing energy for all these blocks becomes difficult

TENNES ET TELECOMMUNICATIONS

# Introduction (2)

#### Mobile communication devices' issues are critical

- Wireless SoC are as complex as cited

- But the power supply is limited by the battery lifetime

#### Demands for low-power and low-cost products are harder to achieve

- Downscaling energy x integration

⇒ Analog section and RF front-end

- Time-to-market x system complexity

⇒ Improved design and high-level modeling effort

ANTENNES ET TELECOMMUNICATIONS

Introduction (4)

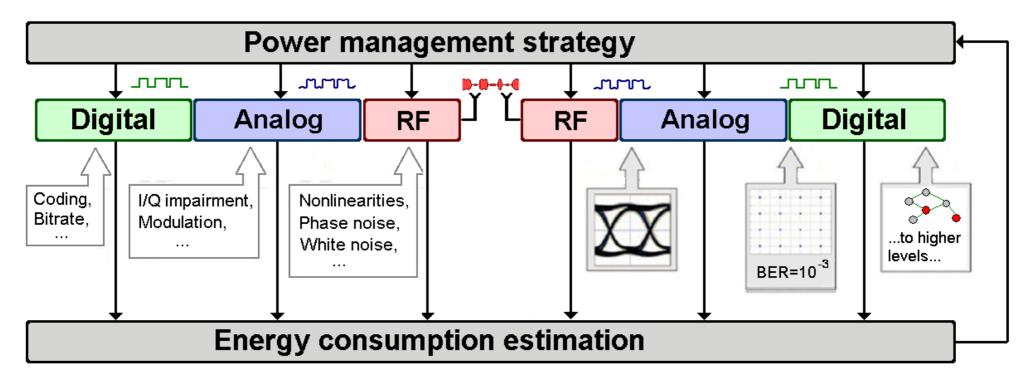

#### What strategy for power management?

ANTENNES ET TELECOMMUNICATIONS

Introduction (5)

#### What strategy for power management?

#### How much energy is consumed by the whole system?

### Introduction (6)

#### RF power amplifier

- Converts low-power into larger RF signal

- Power gain must be efficiently achieved

- Must present good linearity and input/output return loss

- One of most power-consuming block of the transmitter

- Its deeper analysis may be interesting...

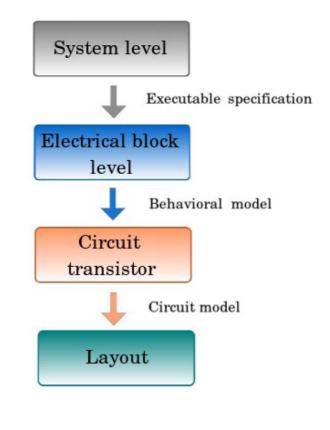

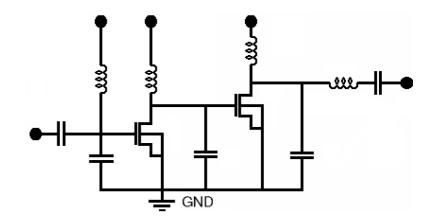

- Hierarchical modeling

- System-Level

- Architectural-level

- Circuit-level

- Layout

7

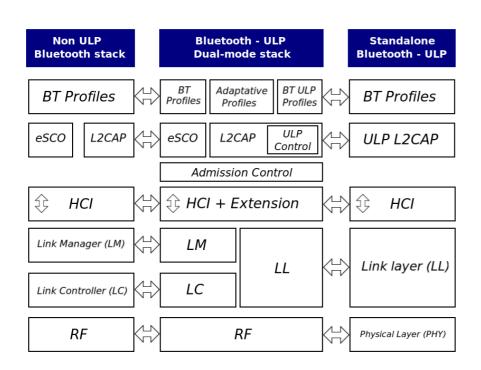

### Power estimation framework

#### Bluetooth LE system

- Low power Low cost applications

- BT backwards compatibility

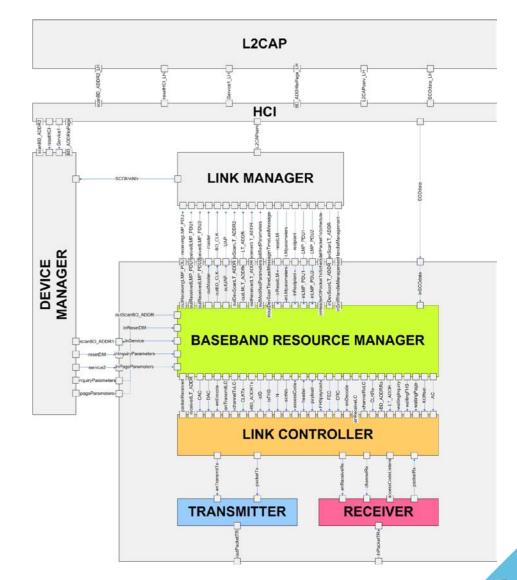

- SystemC high-level model

- L2CAP to bit generation

- Interface to network layer

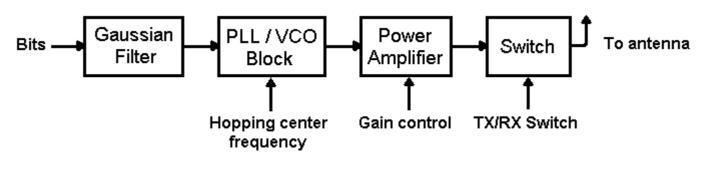

### Power estimation framework (2)

#### RF transmitter

- Direct conversion

- Blocks' characteristics extracted from standard specification

- Refined Commlib RF models

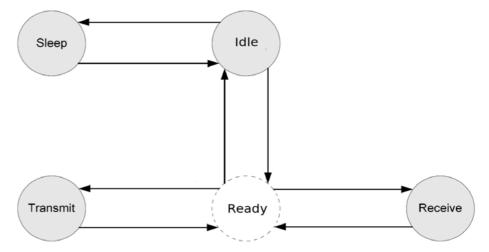

#### BT LE state-machine

- Blocks are not always active

- On/Off switching can be implemented

- Supply network must allow it

- First idea on power consumption during time

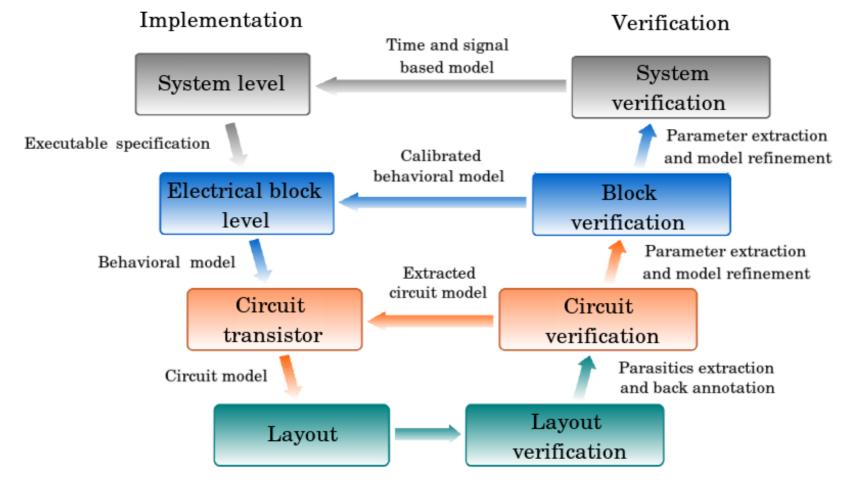

Top-down implementation

#### Mixed signal top-down design methodology

- System specification -> detailed design

- Multi-level modeling and simulation compatibility

- Mentor Graphics AdvanceMS environment

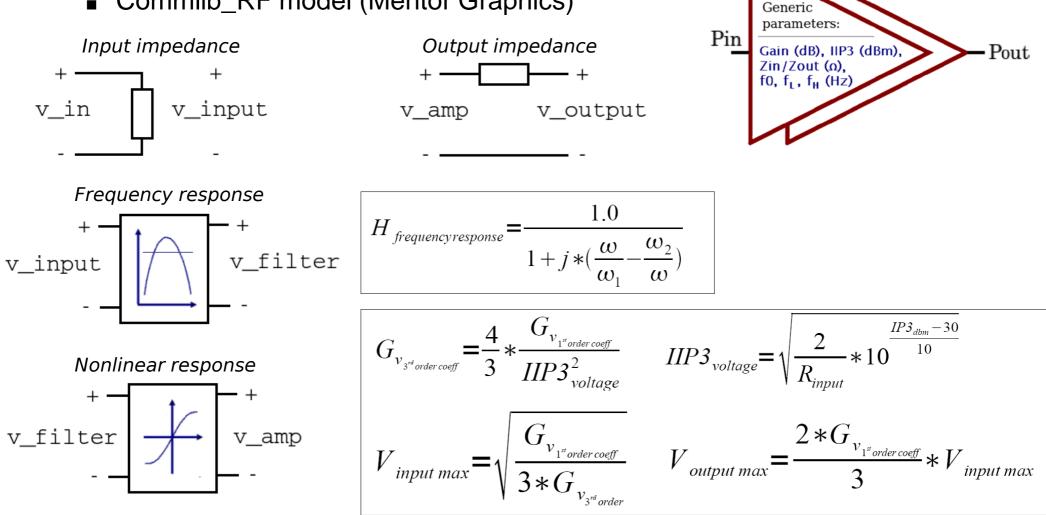

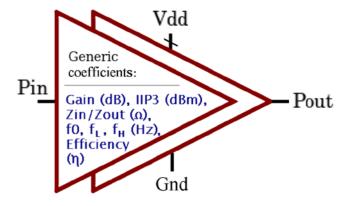

# Hierarchical modeling (2)

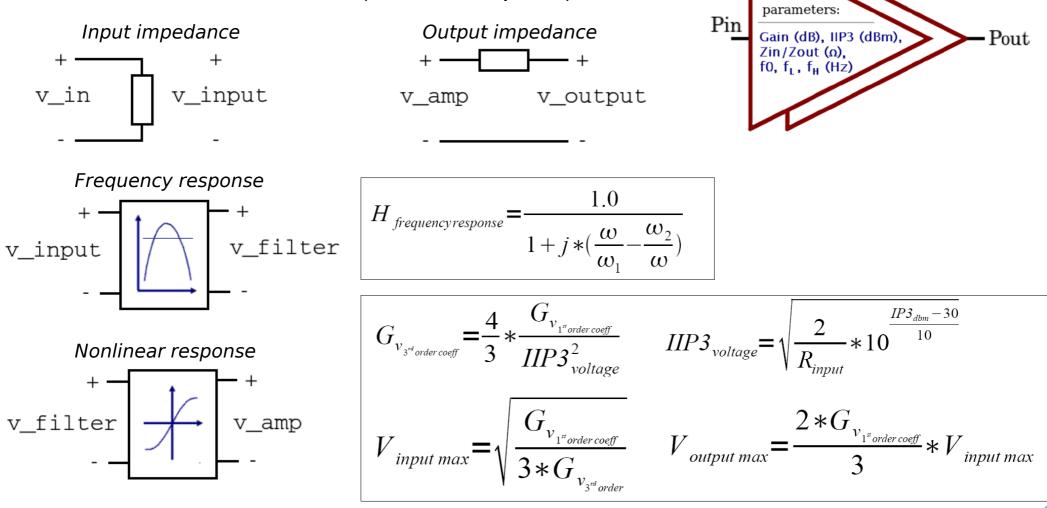

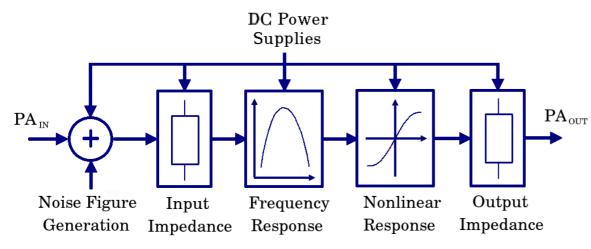

- Conservative **behavioral model** (VHDL-AMS)

- Commlib\_RF model (Mentor Graphics)

# Hierarchical modeling (3)

Generic

- Conservative behavioral model (VHDL-AMS)

- Commlib\_RF model (Mentor Graphics)

Power consumption support?

### Hierarchical modeling (4)

- Conservative behavioral model (VHDL-AMS)

- Power-aware model

- Specifications as functions of inputs

14

#### Power consumption modeled as a variable impedance

Power consumption

$$\begin{array}{c} + & & \\ v_{dd} & & \\ - & & \\ \end{array} \right) i_{core} \\ i_{core} \\ r_{eq}(P_{out,v_{dd}}) = \frac{v_{dd}}{i_{core}}$$

$$\eta_{\frac{W_{RMS}}{W_{RMS}}} = \frac{P_{out}}{P_{vdd}} = \frac{I_{load} * V_{load}}{V_{dd} * I_{core}} \rightarrow I_{core} = \frac{(v_{amp} - v_{output}) * v_{output}}{Z_{out} * V_{dd} * \eta}$$

$$P_{out} = I_{load} * V_{load} = \frac{(v_{amp} - v_{output})}{Z_{out}} * v_{output}$$

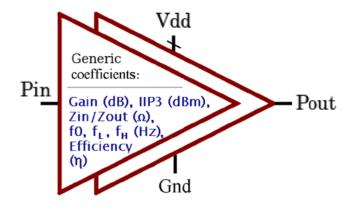

### Hierarchical modeling (5)

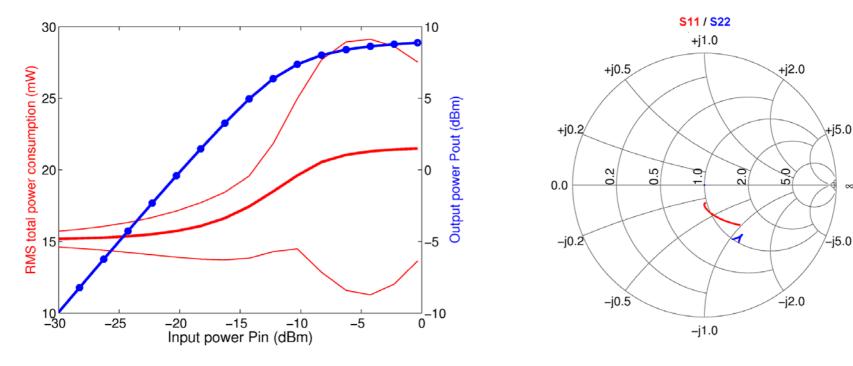

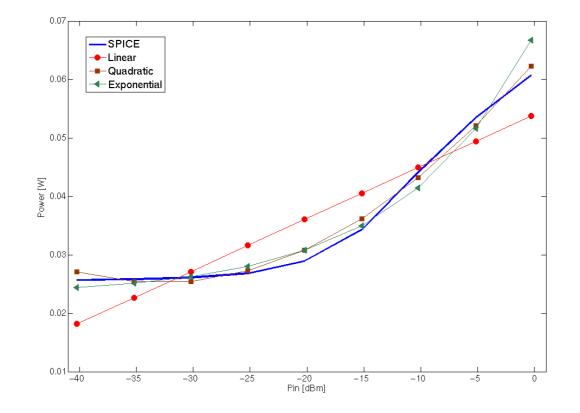

- **SPICE** circuit

- Class-E topology

- Exhaustive simulation for energy-consumption analysis

- Wide input power range (ISM band)

- DC supplies sweep

In order to fully characterize block's specifications

$\infty$

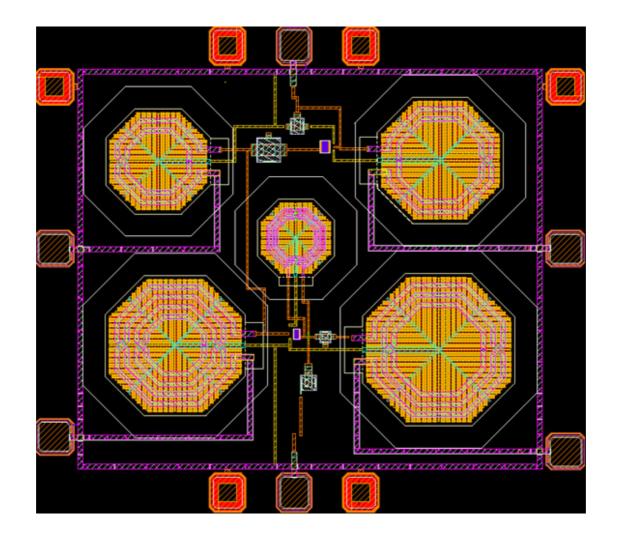

# Hierarchical modeling (6)

- Physical layout of the proposed circuit (Nov 2010)

- Model could include post-layout and measured data

# Hierarchical modeling (7)

- Refined conservative behavioral model (VHDL-AMS)

- Power-aware model

- Specifications as functions of inputs

- Different fitting functions can be tested

### Conclusions

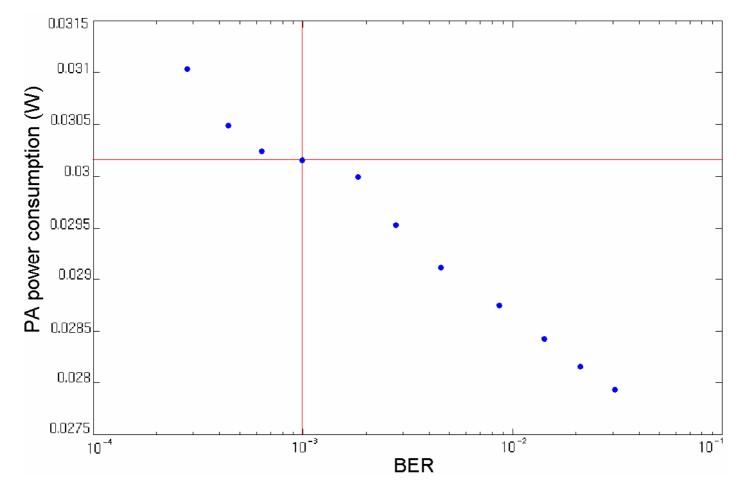

- Hierarchical modeling support within an unified simulation environment has been presented

- **System-level simulation** allowing power consumption estimation

- Able to relate system's robustness to power consumption (e.g., BER)

### Conclusions

#### Main drawbacks

- Need for SPICE electrical information

- Electrical extraction -> model refinement

- Lack of generic power consumption models

- Deeply related to circuit topology

- Genericity ← → Accuracy

# Thanks for your attention!

*Lucas Alves da Silva Lucas.AlvesDaSilva@Unice.fr LEAT - UMR CNRS UNS 6071 Sophia Antipolis - France*